# Wireless Data Acquisition System (wDAQ)

DESIGN DOCUMENT

Team 19 Client: Avishek Das Advisor: Manojit Pramanik Team Members: Lisa Tordai (Software), Henry Chamberlain

(Electrical), Adam Shoberg (Electrical), Vaughn Miller (Computer) Team Email: sddec2419@iastate.edu

Team Website: https://sddec24-19.sd.ece.iastate.edu/

## **Executive Summary**

## Development Standards & Practices Used

- IEEE 802.15.1-2002 (Bluetooth)

- IEEE 802.11 (Wi-Fi)

- IEEE 1118.1 1990 (Microcontroller Programming)

- IEEE Citation Format (References)

- ACM Code of Ethics

- Clean Coding Practices

- Surface-Mount PCB Assembly

## Summary of Requirements

- Compact Size & Mobility

- Wireless Computer or Mobile Connectivity

- Accurate Data Representation

- Longevity & Reliability

- Ease of Use

- Reasonable Production Cost & Pricing

## Applicable Courses from Iowa State University Curriculum

- EE 2010: Electric Circuits

- EE 2240: Signals and Systems I

- EE 2300: Electronic Circuits and Systems

- EE 3300: Integrated Electronics

- CprE 2880: Embedded Systems I: Introduction

- ABE 271/272: 3D Modeling

## New Skills/Knowledge acquired that was not taught in courses

- Schematic & PCB Design

- Soldering

- Wireless Communication Modules

- LabVIEW Programming

## Table of Contents

| 1.  | Introduction                                                      | 5    |

|-----|-------------------------------------------------------------------|------|

| 1   | .1. Problem Statement                                             | 5    |

| 1   | .2. Intended Users                                                | 5    |

| 2.  | Requirements, Constraints, And Standards                          | 6    |

| 2   | 2.1. Requirements & Constraints                                   | 6    |

| 2   | 2.2. Engineering Standards                                        | 7    |

| 3 P | roject Plan                                                       | 7    |

|     | 3.1 Project Management/Tracking Procedures                        | 7    |

|     | 3.2 Task Decomposition                                            | 8    |

|     | 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria | 9    |

|     | 3.4 Project Timeline/Schedule                                     | 11   |

|     | 3.5 Risks And Risk Management/Mitigation                          | . 14 |

|     | 3.6 Personnel Effort Requirements                                 | . 16 |

|     | 3.7 Other Resource Requirements                                   | . 18 |

| 4 l | Design                                                            | .20  |

| 2   | 1.1 Design Context                                                | .20  |

|     | 4.1.1 Broader Context                                             | .20  |

|     | 4.1.2 Prior Work/Solutions                                        | . 21 |

|     | 4.1.3 Technical Complexity                                        | .23  |

| 2   | 1.2 Design Exploration                                            | .24  |

|     | 4.2.1 Design Decisions                                            | .24  |

|     | 4.2.2 Ideation                                                    | .25  |

|     | 4.2.3 Decision-Making and Trade-Off                               | .26  |

| 2   | 1.3 Proposed Design                                               | .27  |

|     | 4.3.1 Overview                                                    | .27  |

|     | 4.3.2 Detailed Design and Visual(s)                               | .28  |

|     | 4.3.3 Functionality                                               | .32  |

|     | 4.3.4 Areas of Concern and Development                            | .32  |

| 2   | 1.4 Technology Considerations                                     | •33  |

| 2   | 1.5 Design Analysis                                               | •34  |

| 5   | ۲esting                                                           | ·35  |

|   | 5.1 l            | Jnit Testing                                         |

|---|------------------|------------------------------------------------------|

|   | 5.2              | nterface Testing                                     |

|   | 5.3              | Integration Testing                                  |

|   | 5.4              | System Testing                                       |

|   | 5.5              | Regression Testing                                   |

|   | 5.6              | Acceptance Testing                                   |

|   | 5.7              | Results                                              |

| 6 | Imp              | lementation                                          |

| 7 | Pro              | fessional Responsibility                             |

|   | 7.1              | Areas of Responsibility                              |

|   | 7.2              | Project Specific Professional Responsibility Areas43 |

|   | 7.3 <sup>]</sup> | Most Applicable Professional Responsibility Area43   |

| 8 | Clos             | sing Material                                        |

|   | 8.1 I            | Discussion                                           |

|   | 8.2              | Conclusion                                           |

|   | 8.3              | References                                           |

|   | 8.4              | Appendices45                                         |

| 9 | Tear             | n45                                                  |

|   | 9.3              | Skill Sets covered by the Team                       |

|   | 9.4              | Project Management Style Adopted by the team         |

|   | 9.5              | Initial Project Management Roles                     |

|   | 9                | .6 Team Contract                                     |

## List of Figures & Tables

#### Figures (Images and Diagrams)

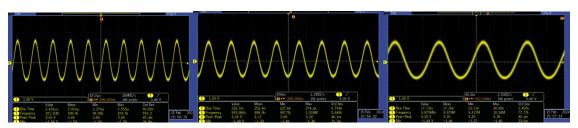

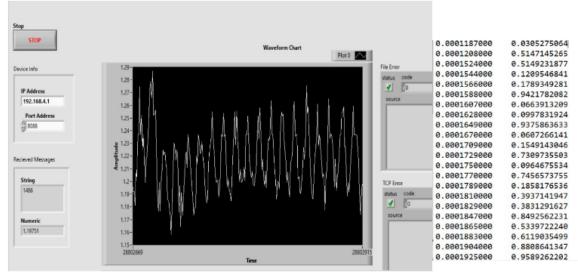

Figure 1: Design Task Decomposition Flowchart Figure 2: Gantt Chart for Section 3.2 Targets Figure 3: IkaLogic IkaScope WS200 [1] Figure 4: Digilent Analog Discovery 3 [2] *Figure 5: Pokit Pro [3]* Figure 6: Lotus Blossom for Wireless Communication Figure 7: Input-Output Relationship for an Analog-to-Digital Converter (ADC) [1] Figure 8: Schematic of the Low-Noise Amplifier & Filtering Circuit Figure 9: Schematic of the ADC and Differential Driving Circuit Figure 10: Minimal STM Circuit for Pin-Compatible F4 MCU Figure 11: ESP32 Wi-Fi Module *Figure 12: Block Diagram of the Process Flow (Split into Two Rows)* Figure 13: Visual demonstration of how the PAT system operates [2] Figures 14, 15, and 16: Output Waveforms for the Low-Noise Amplifier at Frequencies of 100 kHz, 1 MHz, and 10 MHz (Left to Right) Figure 17: Plot of Voltage Values Over Time Obtained from Data in LabVIEW <u>Tables</u> Table 1: Current Monthly Schedule Table 2: Risks, Severities, and Probabilities Table 3: Personnel Effort Requirements Table 4: Public Health, Societal, Environmental, and Economic Considerations Table 5: Pros and Cons Table Developed Through Market Research

Table 6: Weighted Decision Matrix

Image: Constraint of the second se

Table 7: Similarities and Differences Between IEEE's and NSPE's Codes of Ethics [7] [8]

Table 8: Project-Specific Areas of Professional Responsibility

### 1. Introduction

#### 1.1. PROBLEM STATEMENT

Most modern data acquisition systems, also known as oscilloscopes, require BNC cables to connect to and analyze electrical and physical signals. BNC cables are a type of coaxial cable, which are essentially cords that carry an electrical conductor, surrounded by a protective outer layer, to transmit electrical signals from an electrical circuit or physical body to an external device (i.e., the oscilloscope or data acquisition system) for analysis. In addition to these hefty cables, which are often over two feet long, the data acquisition systems require a corded power supply, and they typically use a built-in graphical display to view signals, as well as physical buttons and knobs to adjust display settings, which take up space and increase the size of the device. The combination of cables, power cords, buttons, and display screens make traditional oscilloscopes and data acquisition systems bulky, heavy devices that are not friendly for mobile data gathering (e.g., attempting to monitor an electrical or physical signal outside of a lab setting) or applications of data acquisition devices within larger systems.

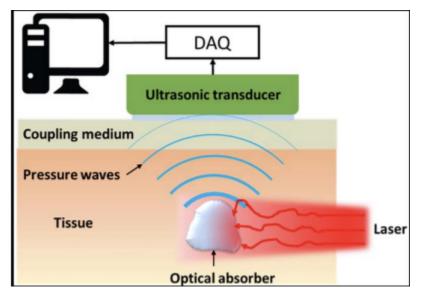

To tackle the size and mobility constraints associated with commercial oscilloscopes, our team wants to create a wireless data acquisition system, powered by a rechargeable battery, that enables mobile real-time data communication using Wi-Fi and is compact enough to fit in about a 1"x5" space. The reason we are striving for mobile capabilities and a small size for our device is because it will be used within a Photoacoustic Tomography (PAT) system in the Biomedical Imaging Laboratory at Iowa State University. A PAT system is a noninvasive device used for biomedical imaging that enables the physical anatomy, oxygen and blood levels, and other biological properties of animals and humans to be identified, like an ultrasound. (ISU's lab will be using the device on small animals.) To accompany the data acquisition device, our team will create a graphical user interface in a software called LabVIEW that enables users to view and analyze data from an external source (e.g., a computer or tablet).

By developing a Wi-Fi connected, battery-powered device that is compatible with external software for data analysis, our team will eliminate the need for BNC cables, power cords, and physical buttons in an oscilloscope and, consequently, be able to easily integrate data acquisition technologies within a larger application.

#### **1.2.** INTENDED USERS

Currently, our project's end user is Iowa State University's Biomedical Imaging Laboratory (BILab), which will use the device for medical imaging on small animals. The laboratory users are likely to be fairly skilled with traditional oscilloscopes and quick to pick up on the new technologies. Looking ahead, the goal is for our device to be applied to a larger user base, from research facilities to educational environments. Some of the potential user groups associated with these include Researchers, Lab Assistants, and Educational Institutions, which are described below.

#### <u>Researchers</u>

Researchers and scientists will be regular users of our device. These users are highly educated, experienced in a lab setting and with lab equipment, and familiar with data collection and analysis techniques. Their needs include accurate data collection and analysis, mobility and portability of

data analysis within and outside of the lab, and a quick, efficient device. Our device would offer many benefits to the user, such as saving lab space, increasing mobility within and beyond the lab space, and new technology to effectively collect and analyze data.

#### Lab Assistants

Our second user group, lab assistants, is another common user; however, their background experience and education may be significantly less than that of a lead researcher. They would need a tool that is easy and relatively fast to learn and become familiar with. Their experience with technology and data analysis may be highly limited, so the device would need to be user-friendly and provide clear, comprehensible data analysis. They would benefit greatly from having an easily accessible tool to help them complete tasks and gather measurements.

#### **Educational Institutions**

This is a device that can be used within educational institutions' research or even lab coursework. These institutions could be colleges, universities, or educational training programs for professionals. Users would need educational tools that facilitate teaching and learning for research practices. They would need live data for students to analyze and comprehend. Our device could provide an affordable solution for educational institutions to provide valuable tools to instructors and students.

Lastly, see <u>Appendix 1.2</u> for User Personas, Empathy Maps, and Journey Maps.

## 2. Requirements, Constraints, And Standards

#### 2.1. REQUIREMENTS & CONSTRAINTS

The key requirements for our design include the following: compact size and mobility (constraint), wireless laptop communication, accuracy and reliability of results, and longevity. On the physical side, the device will need to be compact and convenient for mobile applications. The device will initially be used to explore small animals' anatomy and physical makeup & health, as part of a photoacoustic tomography (PAT) system in the ISU Biomedical Imaging Laboratory (BILab), and up to 20 copies of the device will be connected to transducers (devices that convert physical signals to electrical signals) in a circular configuration. Because of the number of devices that will need to fit within the PAT system, the size of the devices is constrained to an approximately 1" by 1" by 5" volume. Furthermore, since the devices will be rotating and moving continuously, they will also need to be wireless to prevent cord entanglement.

In the way of the user interface and experience, we will need the device to be Wi-Fi connected to enable wireless communication with the user interface and control software on a computer or mobile device, as well as be easy to use. The wireless connection requirement also ties into the physical constraints of the device because there will not be space on the PAT system for the traditional features of an oscilloscope. Most scopes contain a graphical display with buttons to view and analyze signals, but with our device's application, having a display on each individual scope would be redundant, and there is no way that the buttons and display would be able to fit in a 1" by 5" space. It makes much more sense to have a single software program where the user can

view and adjust signals from all scopes (up to 20) at once, which can be best achieved by wirelessly connecting the scopes to the software program, so this is one of the key requirements. For ease of use, we want to make sure the device is easily accessible to all, which means creating a product that can be used by lab technicians and amateur users alike. We will want the user interface to be straightforward and easy to use, as well as ensure the device can easily be connected physically to the PAT system and wirelessly to the user software. This way, newer lab employees and non-technical users will all be able to utilize our product.

The main functional requirement of our device is to obtain accurate and reliable results. This requirement is somewhat vague and difficult to quantify because there is always a possibility of error in results, even if the results are consistent between devices and trials. One way we can more easily gauge the accuracy and reliability of our device is by ensuring we are meeting the specifications in the project proposal. We have slightly modified the requirements, but we are looking to create an RF (MHz frequency range) signal with an amplitude of 1 V (peak-to-peak) and a rise time in the range of around 5 µs. Additionally, we are looking for an ADC with a 12-bit resolution and a sampling rate of at least 100 MS/s (million samples per second). For transmission to the user interface, we want to have a data rate of over 100 Mbps (megabits per second) to ensure fast transmission of results. By creating a device that meets all or most of these specifications, we will be much more likely to have a product that gathers and transmits data accurately and consistently.

The last major requirement for our device, longevity, ties into economic and environmental applications, as well as resource requirements. We will want the device to be durable and long-lasting, because it will be duplicated up to 20 times and used in a larger application for data acquisition. If the device we create breaks easily or becomes less reliable over time, we may need to recreate a higher quality product, which will cost us time, money, and resources, and delay the use of the PAT system until the DAQ systems can be fixed. Also, we would waste significant resources and discard old products, which would have an environmental cost. By creating a quality product from the start that is likely to last for several years, we can avoid complications in the long term.

#### 2.2. ENGINEERING STANDARDS

**IEEE Microcontroller Programming Standard (IEEE 1118.1 1990):** This will likely be used because a major portion of the project is programming the microcontroller to receive the digitized data and perform an action. So, it can be assumed that programmers will need to use this to standardize code and be as efficient with distributed data acquisition.

**IEEE Wi-Fi Protocol (IEEE 802.11):** Our project will use an ESP32 chip that will send data via Wi-Fi to a computer. This device makes use of 802.11 for setting up local area networks and MACs.

## 3 Project Plan

#### 3.1 PROJECT MANAGEMENT/TRACKING PROCEDURES

Our team has adopted an agile project management style. We are trying to complete tasks and milestones for our project in a timely manner to satisfy our client's expectations but are not restricted to a firm timeline. Our client would like the project to be completed a couple of months ahead of the December deadline, because he is hoping to publish an academic paper with us about our project after it is completed. We are currently meeting weekly with our client to discuss our progress, ask questions, and formulate tasks and deliverables for the project as we go, so our timeline is flexible and adaptive to new ideas and design changes. We typically complete design tasks relatively quickly and delegate electrical and software/computer portions of the design to the respective team members.

This project management style has worked well for our team so far, because with the wireless data acquisition system we are designing, many of the software and computer-related portions of the device (e.g., Wi-Fi communication, user interface, microcontroller and analog-to-digital converter) can be designed independently of the electrical parts of the device (e.g., the amplifier, signal filtering and processing, and battery power supply), which makes it more practical to split up most tasks, while working together as a team to bring the components of the device together in the top-level design. Additionally, some tasks and design sprints end up taking significantly more or less time than originally anticipated, making it more sensible to adapt to new timelines as needed. Lastly, our client likes to be closely involved with our work and communicate with us regularly, as well as alter the design and timeline for the project occasionally, which makes the agile working style a much more logical choice overall.

In terms of tracking progress, most of our communication and progress updates within our team and client occur through a shared Microsoft Teams channel. We use our Teams channel to communicate regarding weekly meetings and progress, ask questions, and post updates, documents, and deliverables. These posts include weekly progress report PowerPoints, Schematic documents and PCB files, and code files for software items, posted under the "Files" section of our Teams channel. Eventually, most of these deliverables will also be shared on our team website. Aside from Teams, our team has a Snapchat group chat for casual communication, and we use Outlook and Zoom for communication with our faculty advisor. We have been able to work successfully so far without using Git, Trello, Slack, and related project management tools, but we may end up using these to some extent in the future.

#### 3.2 TASK DECOMPOSITION

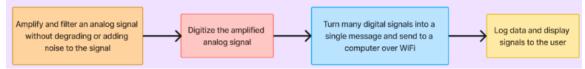

Even though we are using mainly an agile project management style, our project can be split into three major "targets": project planning and design, prototyping, and building the final product. As for specific tasks that must be completed to create the wDAQ device, we need to amplify and filter analog signals (physical signals from test subjects), digitize the signals, send the signals to a computer software user program via Wi-Fi, and display the signals to the user interface. *Figure 1* below shows the design plan and flow that our team created using Figma.

Figure 1: Design Task Decomposition Flowchart

Our team will reference this flowchart throughout the year for a high-level overview of the requirements and deliverables we want to create, but on a smaller scale, we can divide the major

phases and targets of the project into smaller tasks. The list below describes the subtasks for each target associated with our design.

#### Target I: Project Planning and Design

- Understand the requirements and needs of the client and users

- Gather inspiration and ideas by exploring related products on the market

- Create a flexible initial plan of work

- Break the design steps from the flowchart into smaller milestones and tasks

- Delegate individual tasks and responsibilities to team members on a weekly basis

- Design the device in small steps or "sprints"

#### **Target II: Prototyping**

- Order parts and electrical components to create a prototype PCB for the device

- Solder PCBs for individual components of the device and connect them with header pins

- Test the PCB to ensure proper electrical connections and functionality

- Develop user software to a functional level and connect software with the device

- Observe and analyze the results of the prototype

- Discuss shortcomings, design errors, and areas of improvement

#### Target III: Final Buildout

- Host an evaluation & feedback session with the client and users of the product

- Analyze user and client feedback to recognize key areas of improvement

- Brainstorm and make decisions as a team on changes needed for the final product

- Gather new materials or parts for the device as needed

- Work out software bugs and ensure the program is working up to a high standard

- Rebuild the device or parts of the device as needed to meet requirements

- Test the final product and ensure accuracy and satisfaction of requirements

As mentioned in the previous section, many aspects of the project will be delegated specifically to electrical, computer, or software team members, as this will enable team members to work in the areas where they are the most comfortable and skilled. Creating a schematic and PCB for the amplification and filtering stages of the circuit, as well as the battery and battery protection system for the power supply, and parts of the analog-to-digital converter (ADC) will be assigned to electrical team members, while the design and testing of the microcontroller and parts of the ADC circuit will be assigned to the computer and software members, and the design of the user interface and Wi-Fi connection will be almost entirely the responsibility of the software team member. When building the device and combining individual parts, all four team members will come together to ensure the device meets all requirements.

#### 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

The milestones, metrics, and performance targets we will be aiming toward with our project are listed below. We separated these targets by steps from our initial design plan because this plan has more concrete metrics and objectives than the "targets" plan from above. Our client will be designing the battery, so we do not have milestones or metrics for this currently.

#### Amplifying and Filtering the Input Signal:

- <u>Milestone A1:</u> The amplifier has a Bandwidth of 100 kHz ~ 1 GHz

- <u>Milestone A2:</u> System Gain of up to 60 dB with low signal degradation

- <u>Milestone A2.1:</u> The amplifiers produce 2 dB of noise at 300 MHz

- <u>Milestone A3:</u> The system draws a current of 70 mA or less (corresponding to a power draw of 864 mW or less with a 12 V power supply)

- <u>Milestone A4:</u> The system has an input impedance of 50  $\Omega$

- <u>Milestone A4.1</u>: The amplifier is connected by SMA cables with impedance of 50  $\Omega$

- <u>Milestone A5:</u> The PCB contains two single-rail IC amplifiers (cascaded together)

- <u>Milestone A5.1:</u> The IC amplifiers are powered by a single 12 V DC supply

- Cascading of amplifiers will occur later when building the full device's circuit

#### Digitizing the Amplified Signal:

- <u>Milestone B1:</u> Suitable ADC has 12 Bits of resolution with sampling rate of 120 M samples/sec to avoid the effects of aliasing

- <u>Milestone B2:</u> The ADC takes differential (positive and negative) signal inputs.

- <u>Milestone B2.1</u>: Differential inputs are sourced from the output signals of the LNA

- <u>Milestone B3</u>: The ADC is supplied by 5 volts, fed from our single 12 V DC supply.

- <u>Milestone B3.1</u>: The ADC supply voltage is adjusted to 5 V using a voltage regulator such as the LM7805 from TI (implemented in ADC driving circuit).

#### Wirelessly Sending Digital Signals to Computer:

- <u>Milestone C1:</u> Obtain communication module parts compatible with our project's needs

- <u>Milestone C1.1</u>: Research and choose one Bluetooth and one Wi-Fi device that fit the needs of our project

- <u>Milestone C2:</u> Testing capabilities of Bluetooth vs. WIFI

- <u>Milestone C2.1</u>: Using Arduino to program Bluetooth module to successfully send and receive data from laptop

- <u>Milestone C2.2:</u> Using ESP32 to program Wi-Fi module to successfully send and receive data from laptop

- <u>Milestone C3:</u> Programming device to send data over server for LabVIEW to be able to receive data

• <u>Milestone C4</u>: Program project microcontroller to send data through the Wi-Fi Module

#### Logging and Displaying Data in User Interface:

- <u>Milestone D1</u>: Discover capabilities of LabVIEW tools to connect with Bluetooth and Wi-Fi

- <u>Milestone D2:</u> Create LabVIEW VI to create a connection with Wi-Fi Module

- <u>Milestone D3:</u> LabVIEW reads in data from LabVIEW server

- o <u>Milestone D3.1</u>: Read in values from Wi-Fi Module

- <u>Milestone D3.2:</u> Display data in a graph for the user to be able to analyze

- <u>Milestone D3.3</u>: Allow user to log and export data

#### 3.4 PROJECT TIMELINE/SCHEDULE

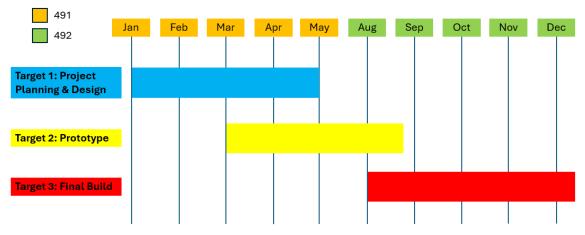

The timeline for our project does not line up with the proposed calendar for projects given in EE/CprE/SE/CybE 491, because our client is pushing us to jump ahead of the recommended schedule and complete the planning & designing quickly, reserving the remaining time in the Spring & Fall for prototyping, revising, building and implementing the final device, and writing an academic paper about the project. This is quite a bit different from the suggested calendar, which recommends using the entire spring semester for designing, planning, and research, and completing the entire implementation and buildout of the project in the Fall semester.

The simplified Gantt chart for our project, split into our three main "targets" described in Section 3.2, is shown below in *Figure 2*. Please note the January work begins January 23; May work ends May 10; August work begins August 26; and December work ends December 13.

Figure 2: Gantt Chart for Section 3.2 Targets

A more detailed monthly schedule for our project that elaborates upon and follows the targets and dates from the Gantt chart is given in *Table 1* below. The schedule also incorporates the

estimated completion dates of specific milestones and metrics from Section 3.3. The tasks and objectives for January through March are finished, but they are included for reference.

| Month                                   | Tasks and Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <u>Month o (January)</u><br>Target 1    | <ul><li>Project Overview</li><li>Team Introductions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| <u>Month 1 (February)</u><br>Target 1   | <ul> <li>Market Research</li> <li>Low-noise-amplifier (LNA) simulation (LTSpice, NI Multisim)</li> <li>Acquisition &amp; testing of prebuilt LNA</li> <li>Extraction of LNA voltage &amp; current characteristics with client <ul> <li>Checking to see if the marketplace LNA follows the metrics/milestones we want for our LNA</li> </ul> </li> <li>Bluetooth and Wi-Fi simulations <ul> <li>Milestones C1, C1.1, C2, C2.1, C2.2</li> </ul> </li> <li>Microcontroller product exploration</li> </ul>                                 |  |  |

| <u>Month 2 (March)</u><br>Targets 1 & 2 | <ul> <li>Microcontroller selection, ordering, and testing of eval board</li> <li>Battery Protection System exploration</li> <li>Microcontroller to Wi-Fi communication testing in LabVIEW <ul> <li>Milestones C3, C4</li> </ul> </li> <li>Develop GUI in LabVIEW <ul> <li>Milestones D1, D2</li> </ul> </li> <li>Sourcing suitable ADC chip <ul> <li>Milestones B1, B2</li> </ul> </li> <li>Schematic and PCB for LNA and ADC circuit in EasyEDA <ul> <li>Milestones A1, A2, A2.1, A3, A4, A4.1, A5.1, B3, B3.1</li> </ul> </li> </ul> |  |  |

|                                                  | Configuration of microcontroller clocks                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Month 3 (April)</u><br>Targets 1 & 2          | <ul> <li>Test and evaluate performance of PCBs for LNA &amp; ADC circuits</li> <li>Revise LNA and ADC circuits if needed</li> <li>Continue developing GUI in LabVIEW <ul> <li>Milestones D3, D3.1, D3.2, D3.3</li> </ul> </li> <li>Design and order PCBs for microcontroller and Wi-Fi circuit</li> </ul>                                                                                    |

| <u>Month 4 (May)</u><br>Target 2                 | <ul> <li>Develop and order (?) battery and battery protection system</li> <li>Connect individual circuits together to form a prototype for the device (exclude battery/battery protection system if unfinished)         <ul> <li>Milestones A5, B2.1</li> </ul> </li> <li>Test and evaluate prototype board</li> <li>Present findings and progress to faculty and industry panels</li> </ul> |

| <u>Month 5 (August)</u><br>Targets 2 & 3         | <ul> <li>Complete battery module and protection system (if not already)</li> <li>Perform power management study and optimization of circuit</li> <li>Revise circuit based on observations and feedback</li> <li>Design PCB (front and back) for final version of the device</li> </ul>                                                                                                       |

| <u>Month 6 (September)</u><br>Target 3           | <ul><li>Order complete PCB (front and back) for the device</li><li>Test final build and troubleshoot</li></ul>                                                                                                                                                                                                                                                                               |

| <u>Month 7 (October)</u><br>Target 3             | <ul><li>Implement the design in PAT system at ISU BILab</li><li>Begin writing an academic paper on the device</li></ul>                                                                                                                                                                                                                                                                      |

| <u>Month 8 (November)</u><br>Target 3 (complete) | <ul><li>Continue writing academic paper</li><li>Complete final design document</li></ul>                                                                                                                                                                                                                                                                                                     |

| <u>Month 9 (December)</u> | Complete and publish academic paper |

|---------------------------|-------------------------------------|

| Target 3 (complete)       | • Present completed project (?)     |

#### Table 1: Current Monthly Schedule

This schedule incorporates the estimated timelines for work and completion of each of our three main "targets", as well as for each of the milestones given in Section 3.3. Although the schedule mentions presenting our project to industry and faculty panels, writing our final design document, and creating & publishing an academic paper on our project, we chose not to classify these as specific targets or milestones, because they are technically not part of our actual project, and we are unsure whether or not we will decide to publish an academic paper.

#### 3.5 RISKS AND RISK MANAGEMENT/MITIGATION

The potential risks associated with each task or "sprint" of our project are given in *Table 2* below, with a severity level and estimated probability assigned to each risk. For risks classified with "high" severity or an estimated probability greater than 0.5, a risk mitigation plan is also given beneath the table.

| Task/Sprint                                | Risk                                                                        | Severity | Probability |

|--------------------------------------------|-----------------------------------------------------------------------------|----------|-------------|

| Amplifier & Filter<br>Design               | Bandwidth of system is narrower than expected                               | Mid      | 0.4         |

| Amplifier & Filter<br>Design               | System gain is less than expected (1)                                       | Low      | 0.6         |

| Wi-Fi Communication<br>Design              | Latency in data from device to GUI (2)                                      | High     | 0.6         |

| GUI (Graphical User<br>Interface) Design   | Having an unstable connection with the Wi-<br>Fi module (3)                 | High     | 0.3         |

| Amplifier & Filter<br>Prototype & Buildout | Some components ordered have incorrect nominal values, tolerances, etc. (4) | Low/Mid  | 0.6         |

| Amplifier & Filter<br>Prototype & Buildout  | Specific components/parts out of stock (5)                                                         | Low/Mid | 0.6 |

|---------------------------------------------|----------------------------------------------------------------------------------------------------|---------|-----|

| Wi-Fi Communication<br>Prototype & Buildout | Wi-Fi module is not compatible to<br>communicate effectively between<br>microprocessor and GUI (6) | High    | 0.7 |

| GUI Prototype &<br>Buildout                 | Missing necessary data and functionality of the user (7)                                           | High    | 0.4 |

| Battery Module                              | Battery protection system doesn't properly protect from overcurrent/overheating (8)                | High    | 0.2 |

| Combined Design &<br>Buildout               | Full design doesn't fit on PCB (9)                                                                 | High    | 0.3 |

| Implementation in<br>BILab                  | Device doesn't fit in the PAT System (10)                                                          | High    | 0.2 |

Table 2: Risks, Severities, and Probabilities

The list below describes the risk mitigation strategies for the risks from the table with high severity or probability above 0.5, which are referenced by (1), (2), etc. in the table.

- 1. <u>System gain is less than expected</u>: The first risk is that the system does not have enough gain to amplify the signal to the required magnitude of the ADC. We have discussed steps to add female header pins so we can add more IC modules in the future to give the system more dynamic and user selected functionality. This would in turn address any problems with system gain.

- 2. <u>Having latency in data from machine to GUI</u>: The device is only useful if the user can see real-time data as a regular oscilloscope would provide. We will need to send over the server a large quantity of data continuously, so we must ensure that the Wi-Fi module we use is capable of this. We also need to ensure the interface we program in LabVIEW will process the data and display it as efficiently as possible.

- 3. <u>Having an unstable connection with the Wi-Fi module</u>: One migration strategy we have currently enacted is the use of high-end Wi-Fi modules that allow for stable connection within a 20-foot radius. Given the condition this device will operate under, it can be assumed that it will give us the needed stability for consistent connection.

- 4. <u>Some components ordered have incorrect nominal values, tolerances, etc.</u>: This is a common mistake when ordering parts that can easily be fixed by verifying the correct values, component properties, etc. with the circuit schematic and placing another order with the corrected parts.

- 5. <u>Specific components or parts are out of stock</u>: Typically, having parts in a design or order that are out of stock can be fixed or worked around easily by substituting parts or components with similar values and characteristics, ordering from another supplier, or purchasing an identical or similar component from a different manufacturer.

- 6. <u>Wi-Fi module is not compatible to communicate between microprocessor and GUI</u>: Proper research using online documentation and product help services will be conducted before the purchase of the device to ensure its compatibility with all components.

- 7. <u>GUI missing necessary data and functionality of the user</u>: The product's main purpose is to serve the user with important information and data analysis. We need to ensure that we are producing the needs of the user in the GUI and that it is easy to collect data.

- 8. <u>Battery protection system doesn't properly protect from overcurrent/overheating</u>: Our client will be handling most issues related to the battery and battery protection system. If the battery is not properly protected from overcurrent or overheating, the consequences could be severe, such as the battery catching fire or exploding. One way these risks could be mitigated is through the use of a voltage regulator in the battery pack (such as the <u>TI</u> <u>LM7805</u>) that keeps the voltage within a safe operating range at all times.

- 9. <u>Full design doesn't fit on PCB (front & back)</u>: If this problem becomes apparent, we will have strategies to remove redundant components and switch footprint sizes of devices.

- 10. <u>Device doesn't fit in the PAT System</u>: To mitigate the risk that the overall device doesn't fit in the designated brackets, we have sectionalized the design into phases and parts while selecting the smallest components that do not reduce overall performance. We have also taken steps to reduce the use of redundant components that were not crucial to the system's performance.

#### 3.6 PERSONNEL EFFORT REQUIREMENTS

| <u>Task/Sprint</u>                               | Hours:<br>Adam | Hours:<br>Henry | Hours:<br>Lisa | Hours:<br>Vaughn |

|--------------------------------------------------|----------------|-----------------|----------------|------------------|

| <b>Planning &amp; Design:</b> Amplifier & Filter | 20             | 20              | 0              | 0                |

| Planning & Design: ADC                           | 10             | 5               | 0              | 5                |

Personnel effort requirements are given in *Table* 3 below.

| <b>Planning &amp; Design:</b> Wireless<br>Communication | 0  | 0  | 20 | 0  |

|---------------------------------------------------------|----|----|----|----|

| Planning & Design: User Interface                       | 0  | 0  | 4  | 0  |

| Prototyping: Amplifier & Filter                         | 20 | 20 | 0  | 0  |

| Prototyping: ADC                                        | 20 | 20 | 0  | 20 |

| Prototyping: Wi-Fi Communication                        | 0  | 0  | 12 | 5  |

| Prototyping: User Interface                             | 0  | 0  | 15 | 0  |

| Prototyping: 3D Model Case                              | 0  | 0  | 15 | 0  |

| Final Build: Amplifier & Filter                         | 15 | 15 | 0  | 0  |

| Final Build: ADC                                        | 15 | 15 | 0  | 15 |

| Final Build: Wi-Fi Communication                        | 0  | 0  | 15 | 15 |

| Final Build: User Interface                             | 0  | 0  | 15 | 15 |

| Final Build: 3D Printing Case                           | 0  | 0  | 5  | 0  |

| Design & Implement Battery Module                       | 10 | 10 | 0  | 0  |

| Implement Device in ISU BILab                           | 5  | 5  | 5  | 5  |

| Write & Publish Paper for Client                        | 5  | 5  | 5  | 5  |

| Presentations for Advisor Meetings | 20  | 20  | 20  | 20  |

|------------------------------------|-----|-----|-----|-----|

| Weekly Client Meetings             | 28  | 28  | 28  | 28  |

| Biweekly Client & Advisor Meetings | 14  | 14  | 14  | 14  |

| Team Website Maintenance           | 0   | 0   | 5   | 0   |

| Prepare Lightning Talks            | 15  | 15  | 15  | 15  |

| Write & Revise Design Document     | 20  | 20  | 20  | 20  |

| Faculty & Industry Panels          | 4   | 4   | 4   | 4   |

| TOTAL HOURS REQUIRED               | 221 | 216 | 217 | 181 |

Table 3: Personnel Effort Requirements

The table above is an estimate for the total number of person-hours that will be required for this project. The table does not include 491 class time, because this time is not considered "hours" where the team is working on the project. However, it does incorporate the time that will be spent outside of class working on presentations and design documents for the course, as well as preparing an academic paper and presentations for our client, meeting with our client and faculty advisor, implementing our device after it is completed, and other tasks and requirements that fall outside of the targets, milestones, and metrics given for the project. Tasks corresponding to the three targets are bolded in the table and milestones are included within these tasks (see schedule from Section 3.4 for explanation of where milestones and metrics fall within each task).

Since our team members have agreed that we do not want to spend more than 10 hours per week on average working on Senior Design, the total available time for each member should be no more than 290 hours (since there will be 29 "working" weeks across the two semesters). As the table shows, the projected hours per member is within this limit, with most members expecting to spend an average of about 7.5 hours per week working on the project.

#### 3.7 OTHER RESOURCE REQUIREMENTS

Aside from the obvious financial resources that will be required to fund our project, we will require tools and equipment, parts and materials, training and instruction, and some amount of labor. A breakdown of our needs associated with each of these resources is given below.

#### • <u>Tools and Equipment:</u>

- Soldering equipment (iron, tin, desoldering wick, flux, wire cutters, clamp)

- Personal protective equipment (safety goggles and gloves for soldering)

- Electrical measuring tools & lab equipment (multimeter, oscilloscope, etc.)

- Software (Arduino IDE, LabVIEW, MATLAB, EasyEDA, NI Multisim, etc.)

- 3D Printer & 3D modeling software

#### • Parts and Materials:

- Resistors, capacitors, and inductors (surface-mount and through-hole)

- Miscellaneous surface-mount and through-hole components

- STM32 Microcontroller IC

- o ESP Wi-Fi Module

- Analog-to-Digital Converter (ADC) IC

- Amplifier ICs (Aside from RF Amplifier)

- o Arduino Board

- Printed Circuit Boards (PCBs)

- Breadboards

- o Jumper Wires

- o SMA Cables

- RF connectors

#### • <u>Training and Instruction:</u>

- EasyEDA and NI Multisim (circuit simulation & design software) tutorials

- LabVIEW training and assistance (as needed)

- Soldering training (as needed)

- General electrical/software questions for client

- <u>Labor:</u>

- ETG Parts Orders

- PCB soldering & assembly (from ETG or JLCPCB)

- Programming microcontroller and LabVIEW

- 3D printing case for assembly

## 4 Design

#### 4.1 DESIGN CONTEXT

#### 4.1.1 Broader Context

Our design problem is currently situated in the relatively limited context of the Biomedical Imaging Laboratory (BILab) at Iowa State University, so lab technicians and research associates will be the main users and parties affected by our design in the immediate future. Looking further ahead, however, we may expand the implementation of our project to different user groups, which would entail a better understanding of the needs of all user parties associated with our product.

The public health, societal, environmental, and economic considerations for our project are given in *Table 4* below.

| Area                             | Description                               | Examples                                  |

|----------------------------------|-------------------------------------------|-------------------------------------------|

| Public health,                   | Our device will not expose users to any   | Electrical risks associated with our      |

| safety, and                      | harmful levels of toxic substances or     | device come primarily from shock          |

| welfare                          | pollutants. There is inherently some      | hazards associated with electrical        |

|                                  | risk associated with using electronic     | components, such as capacitors and        |

|                                  | devices, so users must be conscious of    | battery units. By ensuring users are      |

|                                  | these hazards. Animal research            | trained to take proper electrical safety  |

|                                  | subjects will be analyzed using our       | precautions while working, and that the   |

|                                  | device, but our device will not directly  | device is enclosed by a protective cover, |

|                                  | pose a threat to these animals.           | we can mitigate these risks.              |

| Global,                          | Our project caters to the work styles,    | Implementation of our device will         |

| cultural, and                    | practices, and goals of the workplaces    | require slight changes in our user        |

| social                           | and professions it affects. The device is | community's practices and modes of        |

|                                  | somewhat revolutionary to traditional     | work, but nothing that would be           |

|                                  | lab users in the sense that it is a much  | significant enough to constitute a major  |

|                                  | more compact, portable version of         | overhaul or changed way of thinking,      |

| <b>U</b>                         |                                           | nor a violation of any ethical codes and  |

| accuracy, speca, and case of acc |                                           | values.                                   |

|                                  | through a LabVIEW user interface.         |                                           |

|                                  | Implementation of the device will         |                                           |

|                                  | require a small amount of training and    |                                           |

|                                  | adaptation to the new style of data       |                                           |

|                                  | acquisition, but it should be a quick,    |                                           |

|                                  | smooth transition.                        |                                           |

| Environmental                    | Once implemented, our project has         | Decreasing the usage of materials,        |

|                                  | such a small scope that its               | especially non-recyclable ones,           |

|                                  | environmental impacts will be             | throughout the design and assembly        |

|                                  | minimal. During the design & assembly     | phases of our project will enable us to   |

|                                  | phases of the project, however, some      | minimize the environmental impact of      |

|                                  | unsustainable practices may take place    | our work. Carefully monitoring our        |

|                                  | in the way of procurement &               | inventory of parts and only ordering      |

|          | acquisition of materials, such as over-<br>purchasing and wasting unused<br>materials.                                                                                                                                                                                                                                                                                                                                           | items we need when we need them will<br>yield a higher degree of overall<br>sustainability.                                                                                                                                                                                                                                                                                                                                               |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Economic | Our project is financially viable for our<br>team because most of it is funded<br>through Iowa State University<br>Engineering resources (e.g., ETG). The<br>eventual cost to consumers will<br>depend on the final cost to build the<br>product, along with the device's<br>reproducibility and economies of scale.<br>Once completed, our design may have<br>a considerable impact on the<br>university's financial resources. | The relatively high development cost of<br>our product may create negative<br>financial consequences for the<br>university's engineering departments,<br>which will be funding the bulk of our<br>project, mainly due to the frequent need<br>for parts and materials to build and test<br>prototypes of our device, which we<br>often order in excess supply and<br>sometimes end up scrapping when our<br>design iterations are flawed. |

Table 4: Public Health, Societal, Environmental, and Economic Considerations

#### 4.1.2 Prior Work/Solutions

The background review for our project consisted mainly of market research into products that currently exist which provide similar features or functionality to the device we are striving to procure. We looked at the solutions these companies created, how they related to or differed from our design, and what the advantages or shortcomings of each product and company were. The three similar companies and products we researched are described in detail below.

#### IkaLogic: IkaScope WS200 [1]

The IkaScope WS200 is a data acquisition tool that connects wirelessly to computers (using Wi-Fi) to display signals. Its battery lasts up to a week between charges, it offers relatively similar specifications and performance characteristics to our design at a comparable size, and it is priced at approximately \$250. The manufacturer, IkaLogic, partners with major distributors, such as DigiKey and Mouser, to distribute its products; however, the small size of the company (under ten employees) significantly limits the scope and scale of its operations. *Figure 3* below shows an image of the IkaScope WS200.

#### Digilent: Analog Discovery 3 [2]

The Digilent Analog Discovery 3 is a data acquisition system that connects to computers or similar devices using a USB Type-C connection. It is currently used by multiple ECpE labs at ISU, mainly due to its compatibility with multiple types of software, including MATLAB, LabVIEW, and NI WaveForms. In addition to data acquisition & Analysis, the DAD can also be used in combination with the WaveForms app to function as a signal generator. Digilent, the manufacturer of the DAD,

is a division of National Instruments (NI), which is a large multinational software & hardware corporation, so the company certainly has a leg up in terms of production, product availability, and reputation. Additionally, almost all Digilent devices are compatible with a wide range of new and existing technologies and software tools, and the company offers special discounts to academic user groups, which could make it an advantageous option for universities and research labs to consider. The only major downside to Digilent is the lack of completely wireless connection to its data acquisition devices, as they still require a USB-C connection to computers or other devices for analysis. *Figure 4* below shows an image of the Digilent Analog Discovery 3.

Figure 4: Digilent Analog Discovery 3 [2]

#### Pokit: Pokit Pro [3]

The final company our group researched was Pokit and its wireless data acquisition tool, Pokit Pro. The Pokit Pro utilizes Bluetooth to connect wirelessly to software (rather than Wi-Fi) and it is powered by a USB-C rechargeable battery, as our design is striving to implement for its power supply. The ADC sampling rate and input signal specifications are also quite like our design. One major disadvantage of the Pokit Pro in the context of our application is the fact that it limits signals to a bandwidth of 200 kHz, making it essentially useless for high-frequency (RF) applications like ours. Another disadvantage is simply the use of Bluetooth for data transfer instead of Wi-Fi, because data transfer is generally much slower with Bluetooth than Wi-Fi (sometimes less than ten percent of the data transfer rate), so there will be considerable latency with data transmission for this device compared to our design. As for the manufacturer, Pokit offers numerous other data acquisition and related electrical hardware products for sale, including another data analysis device that is even more compact than Pokit Pro (at the cost of more limited user features), but their devices are not widely available and are somewhat pricey. *Figure 5* below shows an image of the Pokit Pro.

Figure 5: Pokit Pro [3]

*Table 5* below provides a list of pros and cons of our team's solution compared to those of two related product categories on the market: traditional oscilloscopes and existing wireless/mobile data acquisition devices (we chose the Digilent Analog Discovery 2 as our metric for analysis).

|      | Alternative 1: Traditional<br>Oscilloscope                                                                                                                                                                                                                                                           | Alternative 2: Digilent Analog<br>Discovery 2                                                                                                                        | Alternative 3: Our Design                                                                                                                                                                                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pros | <ul> <li>Highly accurate</li> <li>Data sent in real time</li> <li>Wide bandwidth</li> <li>Can read most signals</li> <li>Safe to operate</li> <li>Support functions like math</li> <li>Established documentation</li> </ul>                                                                          | <ul> <li>Compatibility with multiple<br/>types of software</li> <li>NI WaveForms app</li> <li>Many functionalities and<br/>capabilities for data analysis</li> </ul> | <ul> <li>Precise high-frequency data</li> <li>Portable and user-friendly</li> <li>Small size</li> <li>Minimizes use of equipment</li> <li>Likely very inexpensive<br/>compared to similar market<br/>options</li> </ul>                                                                                              |

| Cons | <ul> <li>Fairly costly to acquire<br/>outside of a university<br/>setting</li> <li>Bulky device</li> <li>Requires technical training<br/>or exposure to the device</li> <li>Requires tuning</li> <li>Uses probes (hardwired<br/>connection)</li> <li>Requires corded power<br/>connection</li> </ul> | <ul> <li>Requires USB-C for power<br/>supply and software<br/>connection (not fully<br/>wireless)</li> <li>Larger size than our device</li> </ul>                    | <ul> <li>Small footprint comes at the cost of lower battery capacity and potentially inferior performance</li> <li>Not as fast as high-end portable oscilloscopes</li> <li>No established brand reputation or marketplace presence</li> <li>No customer support or professionally evaluated documentation</li> </ul> |

Table 5: Pros and Cons Table Developed Through Market Research

#### 4.1.3 Technical Complexity

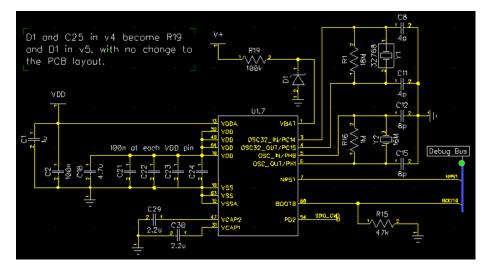

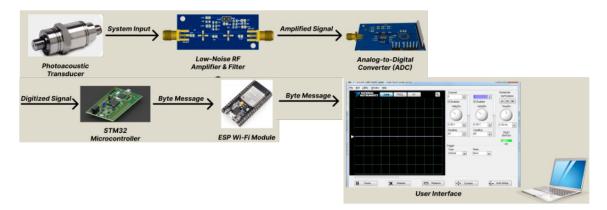

In the way of internal technical complexity, our design incorporates six interconnected components: a transducer, low-noise amplifier, analog-to-digital converter (ADC), microcontroller, Wi-Fi module & connection, and graphical user interface (GUI), each of which leverage a combination of electrical, computer, and software engineering principles. The amplifier manipulates analog signals, using passive components and integrated circuits (ICs) to amplify them; the ADC circuit, which has a specific bit resolution and sampling rate that must be considered in relation to other parts of the design, uses IC amplifiers and passive components to convert the single-ended signal to a differential (double-ended) one, as well as incorporates a linear voltage regulator and DC-DC buck converter that steps down the power supply voltage; the microcontroller and Wi-Fi modules are Systems-on-Chip that are biased and controlled by a larger circuit; the Wi-Fi module transmits data from the microcontroller to the GUI at a fast data transfer rate, and is tested on a breadboard using an Arduino evaluation board; and the GUI, being written in LabVIEW software and connected to the device with Wi-Fi, makes use of primarily software and computer engineering principles in its design & implementation.

On the external side of technical complexity, numerous aspects of our device match or surpass cutting-edge technology in the industry. For one, the use of a rechargeable battery to power an oscilloscope is a novelty, as only a few other devices on the market utilize a rechargeable battery rather than a corded power supply. Next, the compact size of our device beats the size of most oscilloscopes on the market: it will occupy an approximately 1" by 5" by 1" space, making it much smaller than traditional box oscilloscopes. Next, the use of Wi-Fi to communicate data makes our

device one of the fastest in industry, with a data transfer at a rate of up to 150 Mbps (megabits per second), much faster than wireless DAQ systems that utilize Bluetooth communication, which are limited to a data transfer rate closer to 10-20 Mbps. Lastly, the ability to directly "probe" real-world physical signals is a cutting-edge technology: using an SMA connection, our device is directly compatible with transducers, which quickly translate physical signals to electrical signals.

#### 4.2 DESIGN EXPLORATION

#### 4.2.1 Design Decisions

- <u>**Two-stage, single supply voltage low-noise RF amplifier:**</u> Per the decision specifications, the device needs to amplify an input signal from ImV to 1 volt. This required two amplifier ICs, MAR-6SM+, to be cascaded together to achieve the gain required. The device also needs to be biased by a single voltage supply to minimize complexity and size.

- <u>High-speed Microcontroller Unit and separate ADC</u>: Due to the bandwidth requirement, the sample rate of the device needs to be at least 15 million samples per second or higher. An FPGA and ADC would be the best choice if time and money weren't a concern, but a microcontroller-based solution is more familiar and far less expensive, and modern offerings from ST Microelectronics are capable of handling data processing at high speed. The ADC also needs to be as noise free as possible at the frequencies we're working with, so we've chosen to employ a separate ADC IC in series with an STM32 MCU.

- <u>Wireless connection of device to user software:</u> We have decided to go with a Wi-Fi connection (instead of Bluetooth) because Wi-Fi chips allow more data to be transmitted. This allowed the team to narrow down the research of a suitable module. The module of choice ended up being the ESP32 due to its ease of use, low cost, performance matching, and compatibility with other technologies being used in the project.

- <u>EasyEDA for PCB Design</u>: One of the major components of this project is the design of our own PCBs. In the end, we decided to go with EasyEDA for a multitude of reasons, the first being its large library of parts. This minimizes the need for third-party websites to import footprints and other files. The second reason for choosing EasyEDA was its file sharing capabilities. The program allows for team folders, where members can work remotely on the same file. This maximized team collaboration and saved man hours. The last reason EasyEDA was selected for the PCB design was because it was easy to buy the components and PCB directly from the program.

- **Rechargeable battery power supply:** We will be utilizing a rechargeable battery to power our device alongside a battery management system to protect the battery from overcurrent, designed partially by our student team and partially by our client. The battery choice comes down to three potential options: Lithium-ion, Nickel Cadmium (NiCd), and Nickel-Metal Hydride (NIMH), all of which are compact and can be compatible with integrated USB Type-C charging. We will either be designing the battery management system (BMS) or using a preassembled chip, but a study on the power usage of the circuit and power management optimization, which will be completed after designing a prototype of the device (without the battery), will enable us to determine the requirements of the battery and associated BMS. We will also be implementing a voltage regulator (such as TI's

LM<sub>7</sub>805 Linear Regulator IC) with the battery's power supply that will ensure we supply steady DC voltages to the circuits within our design and avoid accidental overcurrent.

#### 4.2.2 Ideation

For each of the key design decisions, our team created a Lotus Blossom Diagram to identify potential options and solutions. The wireless communication aspect of the design process was one of the few areas where our team had more leniency and "options" to choose from in the design, rather than needing to use a specific technology or device to achieve a requirement. The section of the Lotus Blossom Diagram where we identified possible options and design considerations relating to wireless communication is shown in *Figure 6 below*.

| Option 1:<br>Bluetooth                          | <u>Option 2:</u> Wi-Fi         | Data transfer rate<br>(faster = better)        |

|-------------------------------------------------|--------------------------------|------------------------------------------------|

| Connection range<br>(only need a few<br>meters) | H<br>Wireless<br>Communication | Connectivity to<br>laptop (easier =<br>better) |

| Cost of<br>technology                           |                                |                                                |

Figure 6: Lotus Blossom for Wireless Communication

The options, constraints, and considerations our team came up with for wireless communication using the Lotus Blossom technique are described in detail below.

- <u>Bluetooth (Option 1):</u> Bluetooth communication chips have relatively high latencies for wireless communication (30+ ms) and somewhat slow data transfer rates (typically no more than 30 Mbps (megabits per second)). The connection range is also small (typically 10-20 meters or less). The advantages of Bluetooth include mostly reliable & consistent connectivity and secure data transfer.

- <u>Wi-Fi (Option 2)</u>: Wi-Fi communication tends to have a lower latency for wireless communication (often less than 10 ms) and a much higher data transfer rate than Bluetooth (over 100 Mbps), which enables high-speed data collection at all times. The connection range of Wi-Fi chips is also significantly higher than BT chips (~100 meters). Wi-Fi connection is also usually consistent and is highly secure.

- Data Transfer Rate: The data transfer rate of the device is an important factor in the decision for wireless communication because a high data transfer rate ensures fast communication with software and compatibility with the sampling rate of the ADC and clock speed of the MCU. Our ADC of choice (ADC12020 from Texas Instruments) has a sampling rate of at least 20 MS/s (million samples per second), and the MCU (microcontroller) has a clock speed of over 100 MHz, so the technology we use will need a data transfer rate that matches or surpasses these rates to ensure compatibility. This makes Wi-Fi a much more attractive choice already.

- **Connection Range:** The connection range of our wireless communication is not important, because the user will most likely be using the LabVIEW software close to the device (i.e., within a few meters). However, having more flexibility with the distance between the user and the device is always a plus. Wi-Fi chips offer a connection range in excess of 100 meters, while most Bluetooth chips are limited to a connection range of a few (up to 10) meters, which makes Wi-Fi a better option again.

- <u>Ease of Laptop Connectivity:</u> Both technologies are relatively easy to connect to once they have been properly configured. Initial tests of both technologies have shown some connection difficulties and delays, but they typically resolve quickly. From a user perspective, Wi-Fi networks are generally a bit easier and faster to connect with than Bluetooth devices, and the use of a security key makes them a safer data transfer choice.

- <u>Cost of Technology:</u> Most marketplace Bluetooth and Wi-Fi chips are relatively inexpensive (in the range of \$10 to \$20), so there is not a significant discrepancy between the costs of the two technologies, which makes this an unimportant factor in the decision process.

#### 4.2.3 Decision-Making and Trade-Off

For the decision-making and ideation process, our team used a weighted decision matrix to identify the pros and cons of each of the potential options for wireless communications (See *Table 4* below). We selected this option for ideation because it enables us to easily understand the different advantages, disadvantages, and characteristics of Wi-Fi and Bluetooth technology, as well as make more direct comparisons between the two technologies to make a well-informed decision. The process of a weighted decision matrix involves identifying the relevant considerations and factors associated with our two options, assigning a "weight" (importance factor) from 1 to 5 for each factor, and assigning a performance score for each technology and consideration, also from 1 to 5, with an explanation of how well each technology satisfies each of the criteria.

| Factor                | Weight | Wi-Fi                                                                                                    | Bluetooth                                                                                                                     |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Data Transfer<br>rate | 5      | <b>5</b> - Data transfer rate often<br>exceeds 100 Mbps and chips have<br>low data communication latency | <ul> <li>2 - Data transfer is rarely above</li> <li>30 Mbps and some latency exists</li> <li>in data communication</li> </ul> |

| Connection<br>Range            | 2 | <b>4</b> - Connection range is large (more than 100 meters)                                           | <b>2</b> - Connection range is limited (typ. 10-30 meters)    |

|--------------------------------|---|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Ease of Laptop<br>connectivity | 3 | <b>4</b> - Upon configuration of IP<br>addresses, it is as simple as<br>connecting to your home Wi-Fi | <b>4</b> - After configuration,<br>connection is quick & easy |

| Cost of<br>Technology          | 2 | 3 - Cost of chips range from \$10-<br>\$20                                                            | 3 - Cost of chips range from \$10-<br>\$20                    |

|                                |   | Total Weight: 51                                                                                      | Total Weight: 32                                              |

#### Table 6: Weighted Decision Matrix

Note: Based on the weighted matrix, *Table 1*, it is evident that the use of a Wi-Fi chip is the way to go for our project. It scored significantly higher in the most heavily weighted factor, data transfer rate, while staying on par with Bluetooth for every other factor.

#### 4.3 PROPOSED DESIGN

#### 4.3.1 Overview

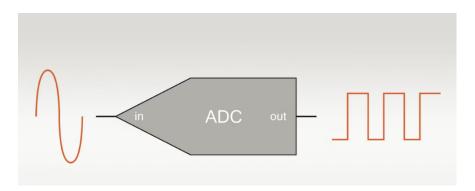

A high-level view of our design is a low-cost, user-friendly, wireless oscilloscope (tool used for viewing properties of signals). The design starts off with a low-strength, high-frequency signal being captured and sent to an amplification and filtration stage. The amplification stage essentially takes this initial signal and scales it by a factor of close to 1000. The purpose of the filtration stage is to remove unwanted components of the signal. Like how a coffee filter works, it removes the unwanted portions of the signal (the "coffee grounds") and passes the portions we do want (the coffee). Following this, the filtered and strengthened signal travels to the analog-to-digital conversion stage. This portion of the device uses components that essentially follow the original signal, but in the form of steps (like staircases). Reference *Figure 7* below for a visual representation of the input-output relationship for an ADC.

Figure 7: Input-Output Relationship for an Analog-to-Digital Converter (ADC) [1]

Once the signal has been digitized, computers can perform actions with the signal. Following the signal's digitization, it travels to a component called a microcontroller. This is the jack of all trades for electronics components. It can perform actions based on user-determined instructions using a component called a central processing unit (CPU). It also has storage space to hold onto information pertaining to the digitized signal. Once the microcontroller has executed its user instructions, it spits the information out of the output pins. The last stage of hardware the information travels to is the Wi-Fi module. Like how you connect to your Wi-Fi at home, a user can connect to the Wi-Fi module on their computer. This is where the information is transferred wirelessly to the computer for the user to see on their computer or mobile device.

#### 4.3.2 Detailed Design and Visual(s)

The design of our device consists of six different interconnected stages that operate in close succession (the first of which is technically not part of the device). A technical description of each of these stages, followed by a block diagram showing images of the individual components and the order of their connections, are given below.

- **Stage 1: Photoacoustic Transducer:** A Photoacoustic Transducer will provide the input signal to each DAQ system that is implemented within the Photoacoustic Tomography (PAT) system, connected by male and female SMA ports. These transducers take physical signals from the real world (in our application, sound waves and echoes from animals) and transmit them to the DAQ devices as electrical signals that can be operated on and analyzed. The transducers have already been designed and implemented within the PAT system, so our team will only be concerned with connecting them to our devices.

- **Stage 2: Low-Noise RF Amplifier & Filter:** The low-noise amplifier takes a 1 mV (peak-to-peak) analog input signal and amplifies it to an amplitude of approximately 1 V (peak-to-peak). Thus, the overall amplifier has a gain of close to 1000 V/V, or 60 dB on a logarithmic scale, which is implemented by cascading two amplifiers with individual gains of approximately 32 V/V (30 dB). We chose the <u>MAR-6SM+</u> amplifier by Mini Circuits for our design. The amplifier is considered "low-noise" because it does not distort the output signal or significantly degrade the signal-to-noise ratio: the noise figure of the amplifier is 2 dB at 300 MHz. Another important characteristic of the amplifier circuit is wide bandwidth: because we want to amplify radio frequency signals per the project proposal, we will require an amplifier bandwidth in the MHz range, which the MAR-6SM+ amplifier offers (with a wideband frequency range from DC to 2 GHz). The operating bandwidth of